AG10KSDE176

AGM AG10KSDE176 是由 AGM FPGA AG10K 与 SDRAM 叠封集成的芯片,具有 AG10K FPGA 的可编程功能,提供更多可编程 IO,同时内部连接大容量 SDRAM。

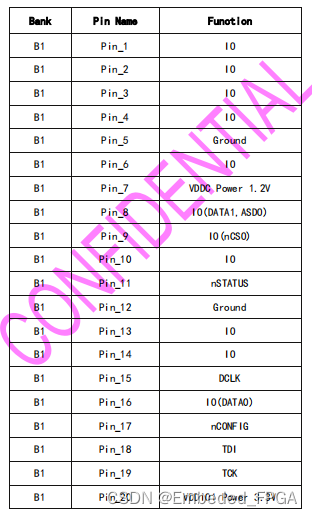

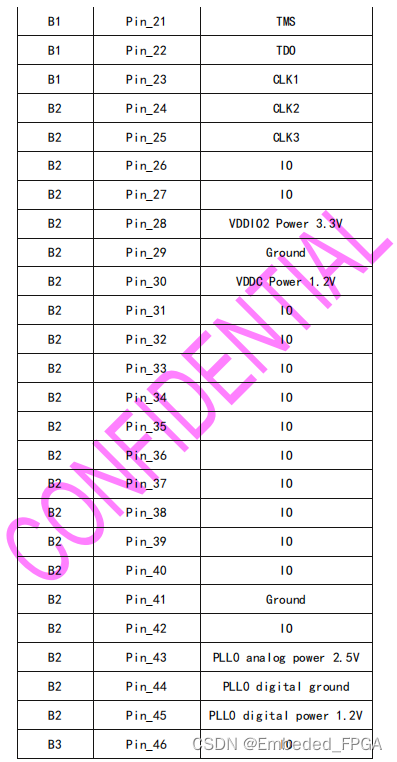

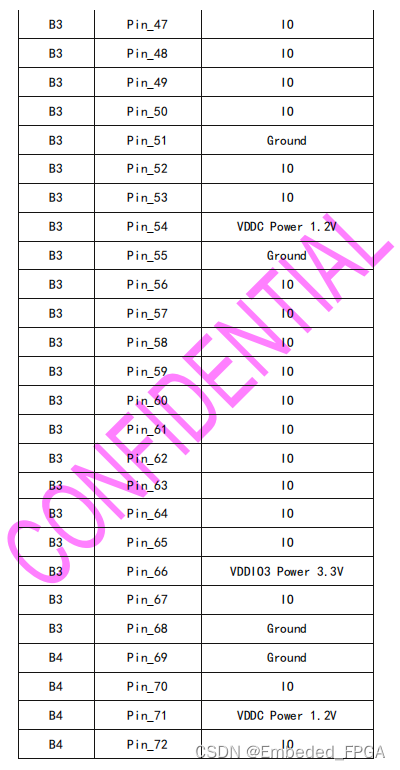

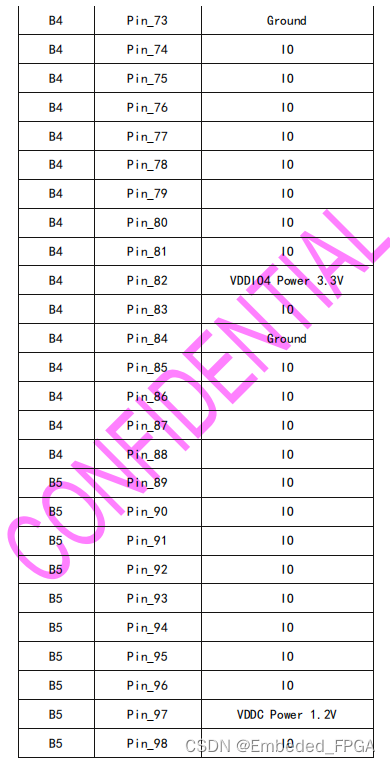

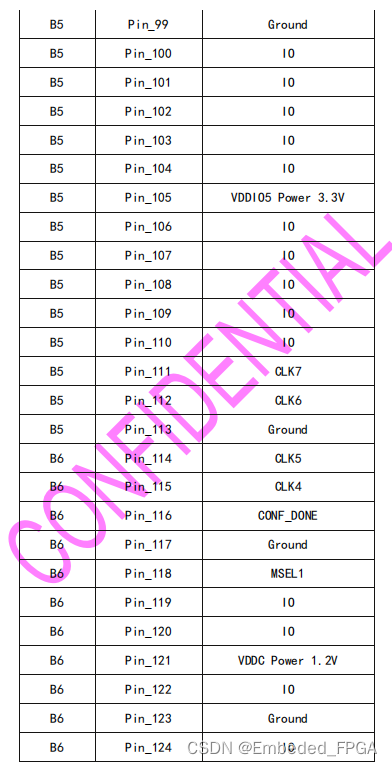

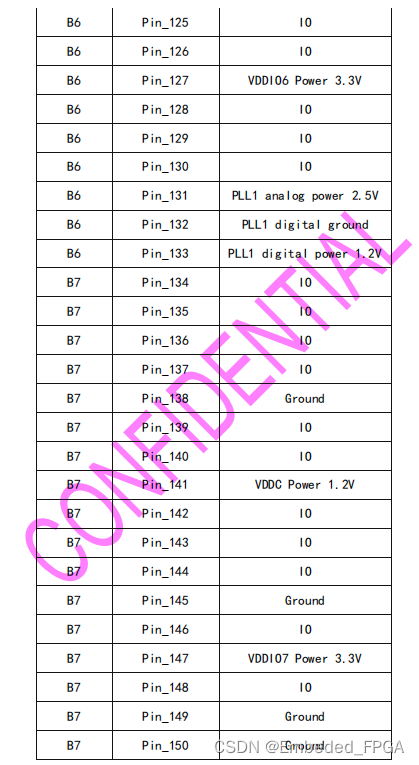

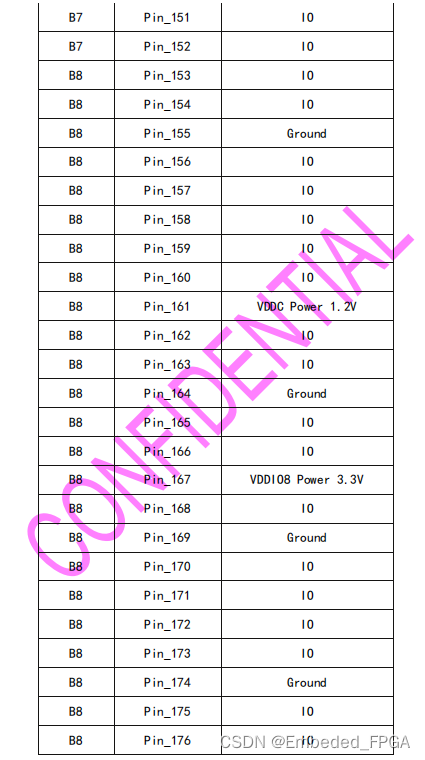

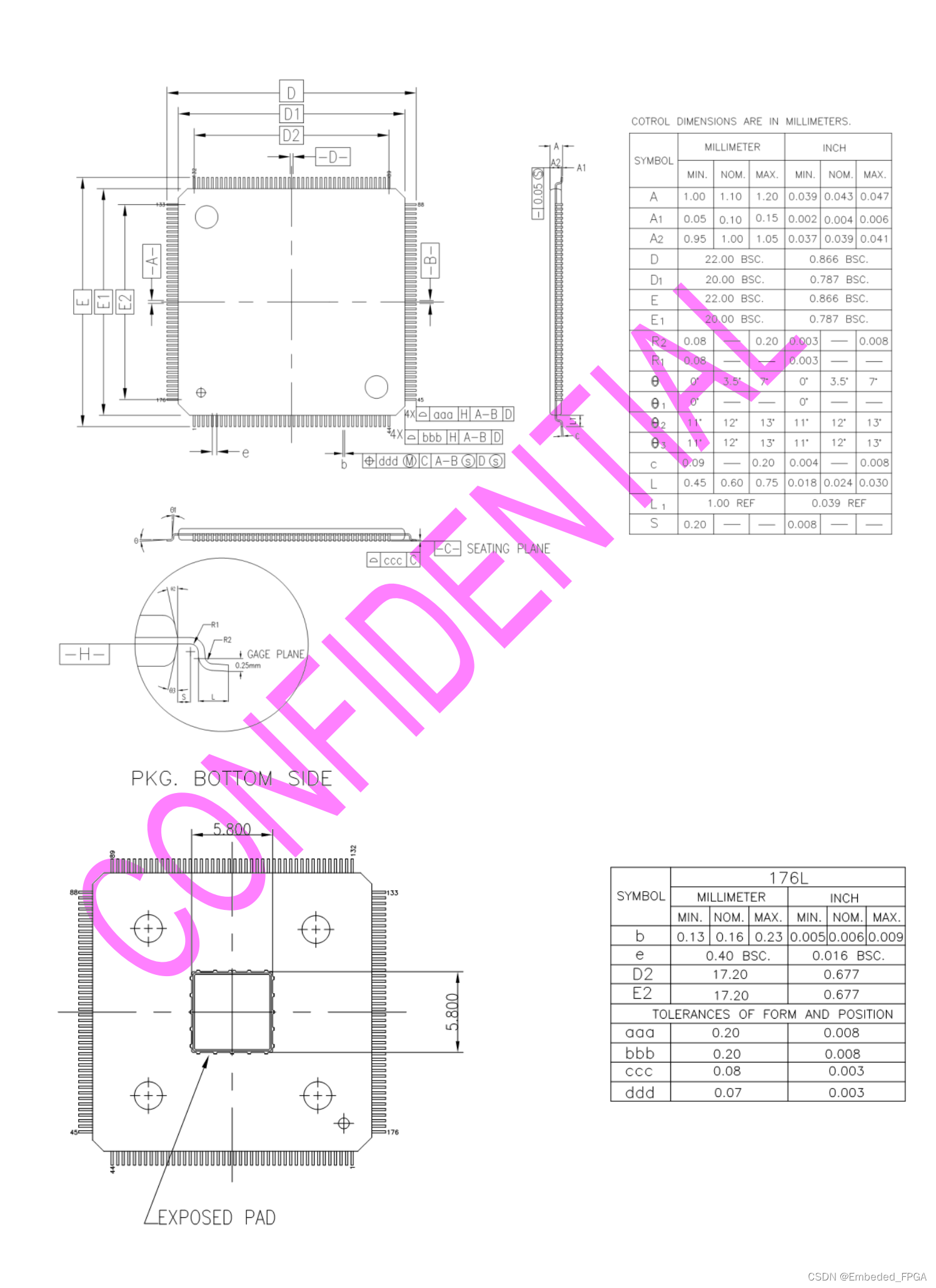

FPGA 外部管脚输出

EQFP176 封装底部 Pad 为 GND,管脚说明请见下表:

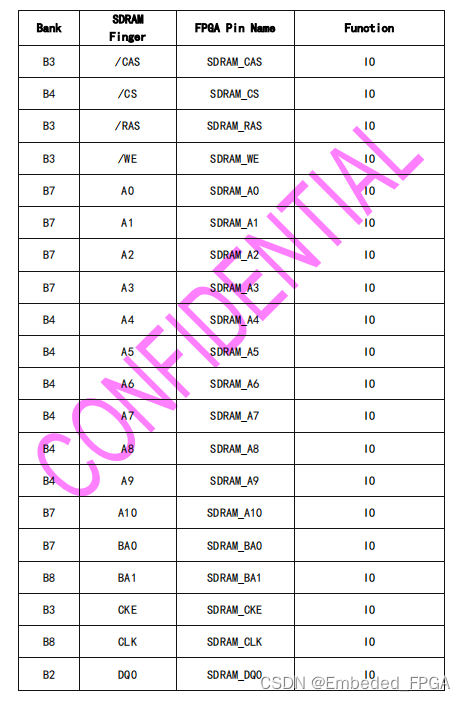

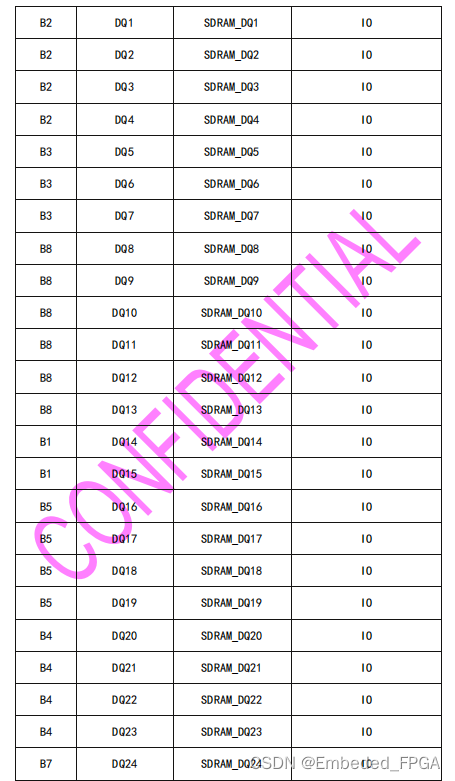

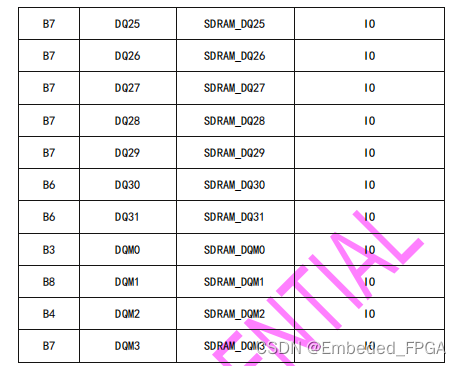

SDRAM 说明

内部 SDRAM 为 64Mbit(512K words × 4 banks × 32 bits)容量。由于 SDRAM 为 3.3V 器件,FPGA 的 VCCIO 也需接 3.3V。

FPGA 的 IO 与 SDRAM 的内部连接,请见下表:

配置说明

AG10K 配置方式支持 JTAG,AS(Master)和 PS(Slave)方式,可通过 MSEL[2…0]选择。

其中 MSEL2 和 MSEL0 已在封装内接到 GND,仅需把外部管脚 MSEL1 按照下表设置,选择不同配置模式。AS 方式也是通过 JTAG 口直接烧写配置 FLASH。

封装图

软件开发流程(Compatible 模式)

用 Quartus 基于 Cyclone IV EP4CE10F17 为基础完成原始设计。管脚位置分配可先忽略。

建一新目录作为 AG10K 的项目目录。

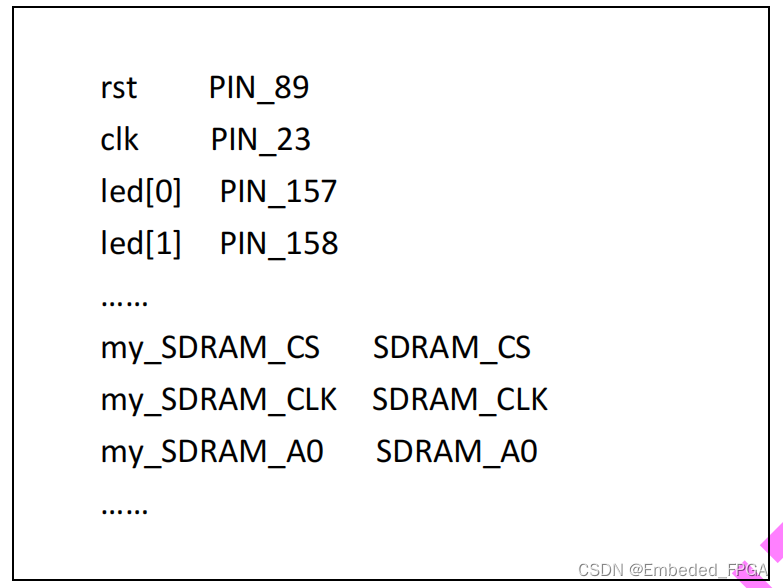

新建一个文本格式的管脚分配文件,命名为.ve。编辑 ve 文件加入 FPGA 的 IO位置设置。管脚名称请参考前面的管脚说明表格,ve 文件格式如下(管脚设计名称+空格+封装管脚名称):

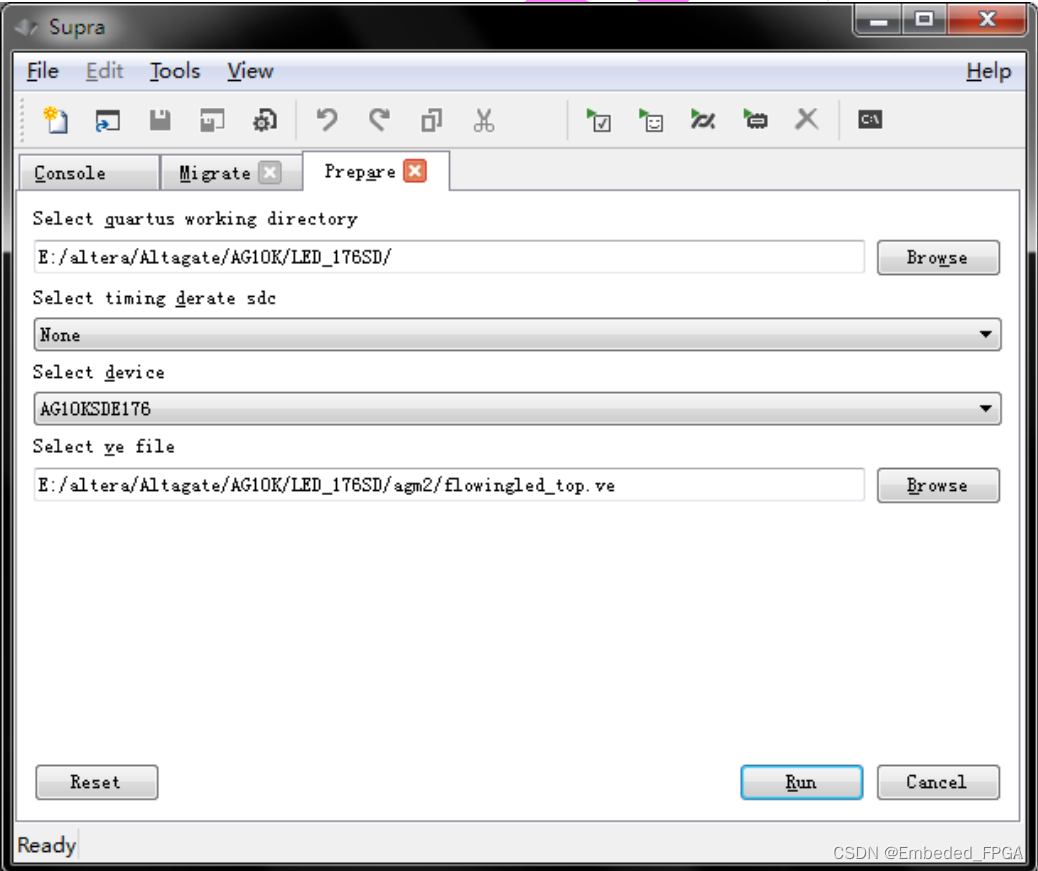

打开 AGM Supra 软件,新建工程,执行 Tools-Prepare。选择 Quartus II 项目目录,Device选 AG10KSDE176,并选择编辑好的 ve 文件后,点击 Run。正确运行后会生成 af_prepare.tcl等文件。

打开 Quartus 项目,通过 Tools-Tcl Scripts 运行 af_prepare.tcl 脚本文件,会把 ve 的内容导入到 EP4CE10 对应的管脚分配,并继续执行编译过程,在项目目录中生成 Simulation目录以及综合后的 vo 等文件。

注意:PIN_38 和 PIN_168 在 F256 里没有对应管脚,所以 Quartus 没有分配,可以忽略。

Supra 会在后面的编译中按照 ve 文件分配到 176 封装的具体管脚。如原 Quartus II 工程中有管脚分配信息,需先删除再执行 TCL。

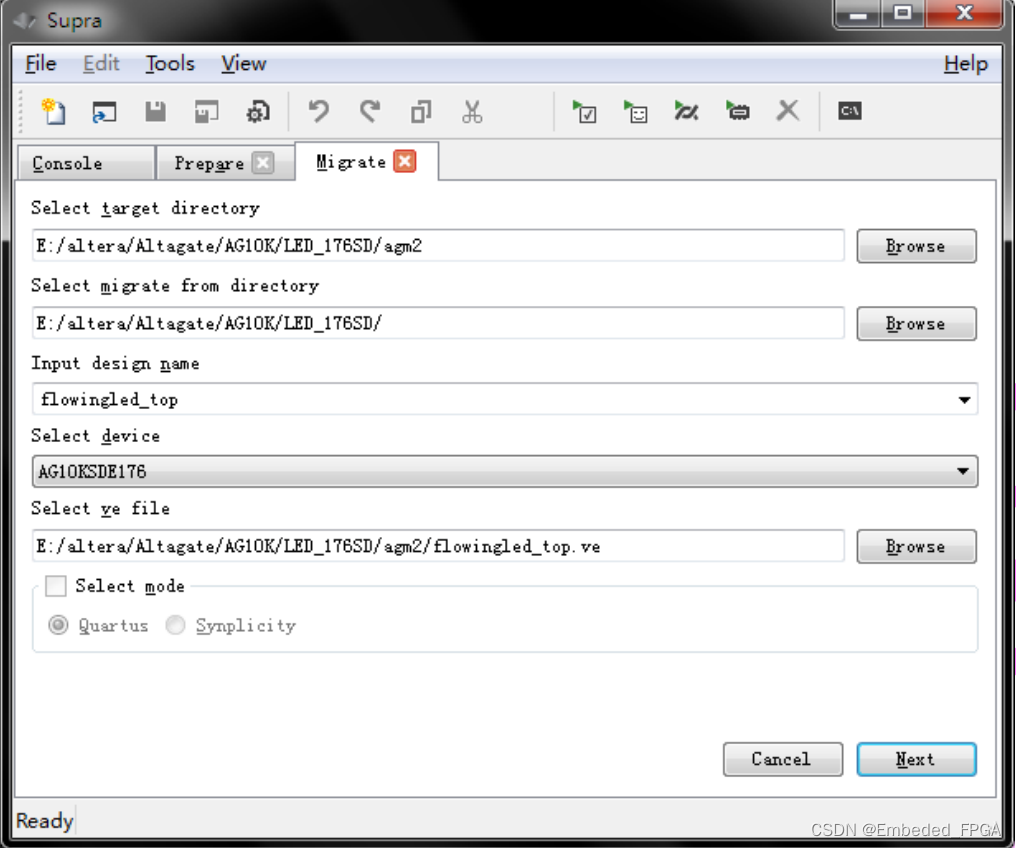

打开 AGM Supra 软件,执行 Tools-Migrate。Target directory 设为 AG10K 的项目目录,From directory 设为原 EP4CE10 的设计目录。选择 Device 为 AG10KSDE176,同样选择 ve 文件。

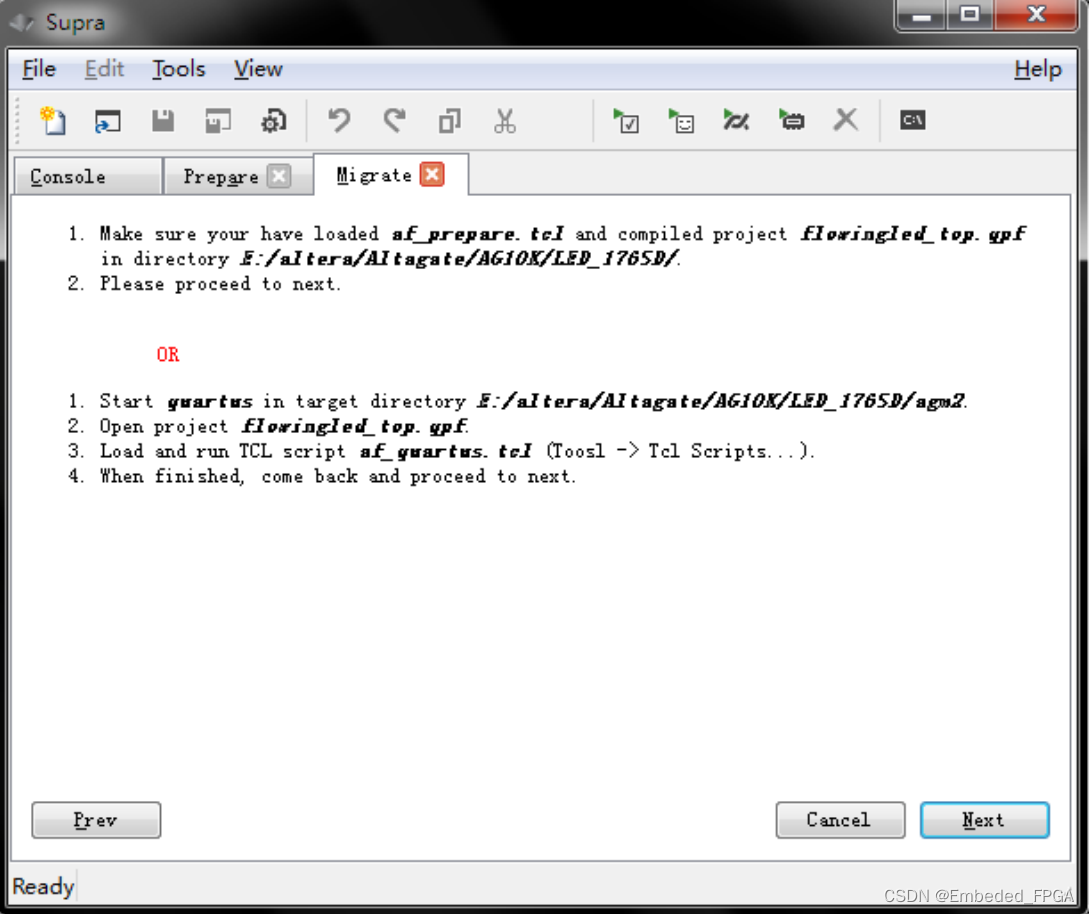

点击 Next,参考页面说明 OR 上面的部分,即直接点击 Next。

下面界面中可设置些编译参数,或采用默认设置即可。

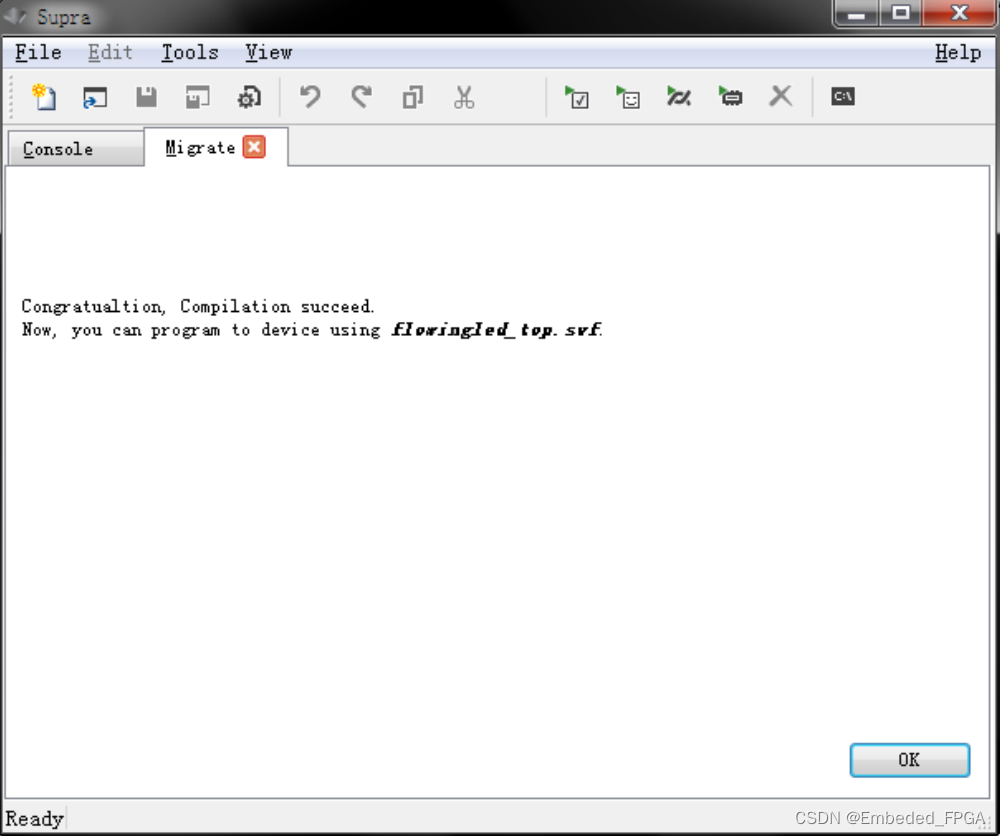

点击 Finish,进入编译过程,在 Console 界面可查看编译信息,成功后显示下面信息,并生成配置烧写文件。

如需修改原设计,由于 af_prepare.tcl 已把设置改好,不用重新执行 tcl,在 Quartus 中直接编译即可。然后在 Supra 中 Compile 界面进行最后编译。

器件烧写

Supra 软件中,选择菜单:Tools-Program。选择需烧写的 PRG 文件,采用默认下载线类型 USB-Blaster。

点击“Program”按钮,开始通过 JTAG 烧写 PCB 上 AG10K 或 FLASH 器件。

烧写文件类型:

_SRAM. prg 文件为片内 SRAM 写入,通过 JTAG 烧写,掉电即失效,可用于设计调试;

_master.prg 文件为 Master(AS)配置方式下,通过 JTAG 烧写 FLASH 的文件;

_master.bin 为 Master(AS)配置方式下,Flash 的通用烧写文件;

.bin 或 rbf 文件为 Slave(PS)配置方式所需文件,rbf 文件的字节高低位反向。

Low Cost and High Performance FPGA with ARM and SDRAM inside

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如若转载,请注明出处:/a/234759.html

如若内容造成侵权/违法违规/事实不符,请联系我们进行投诉反馈qq邮箱809451989@qq.com,一经查实,立即删除!相关文章

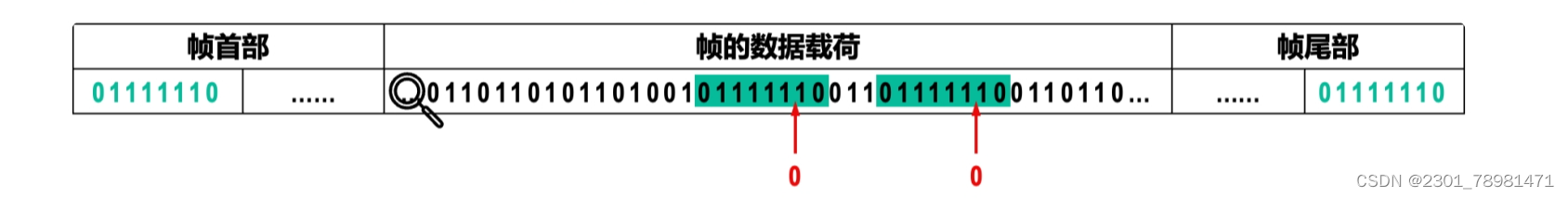

计网Lesson8 - NAT技术与链路层概述

文章目录 NAT 技术1. 因特网的接入方式2. 公网和私网3. NAT 技术 链路层1. 数据链路层概述2. 数据链路层的三个问题2.1 封装成帧2.2 透明传输2.3 差错检测 NAT 技术

1. 因特网的接入方式 光猫将电信号转换为数字信号发送给路由器 光纤入户 光纤传递的就是数字信号,…

uniapp iOS离线打包——运行项目到模拟器报错?

运行项目、打包时报错问题 记录个人在开发过程中遇到的相关问题,后续有时间会不定时更新 文章目录 运行项目、打包时报错问题运行到模拟器报错解决方案 打包报错解决方案 运行到模拟器报错 解决方案

选中项目工程 —> Build Settings 滑动底部 —> User-Defi…

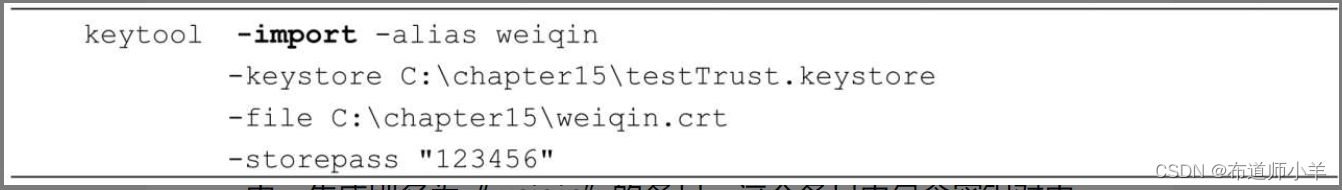

Java网络编程——安全网络通信

在网络上,信息在由源主机到目标主机的传输过程中会经过其他计算机。在一般情况下,中间的计算机不会监听路过的信息。但在使用网上银行或者进行信用卡交易时,网络上的信息有可能被非法分子监听,从而导致个人隐私的泄露。由于Intern…

Leetcode—389.找不同【简单】

2023每日刷题(五十五)

Leetcode—389.找不同 实现代码

char findTheDifference(char* s, char* t) {int len strlen(s);int len2 len 1;int a[26] {0};int b[26] {0};if(len 0) {return t[0];}for(int i 0; i < len; i) {int idx s[i] - a;…

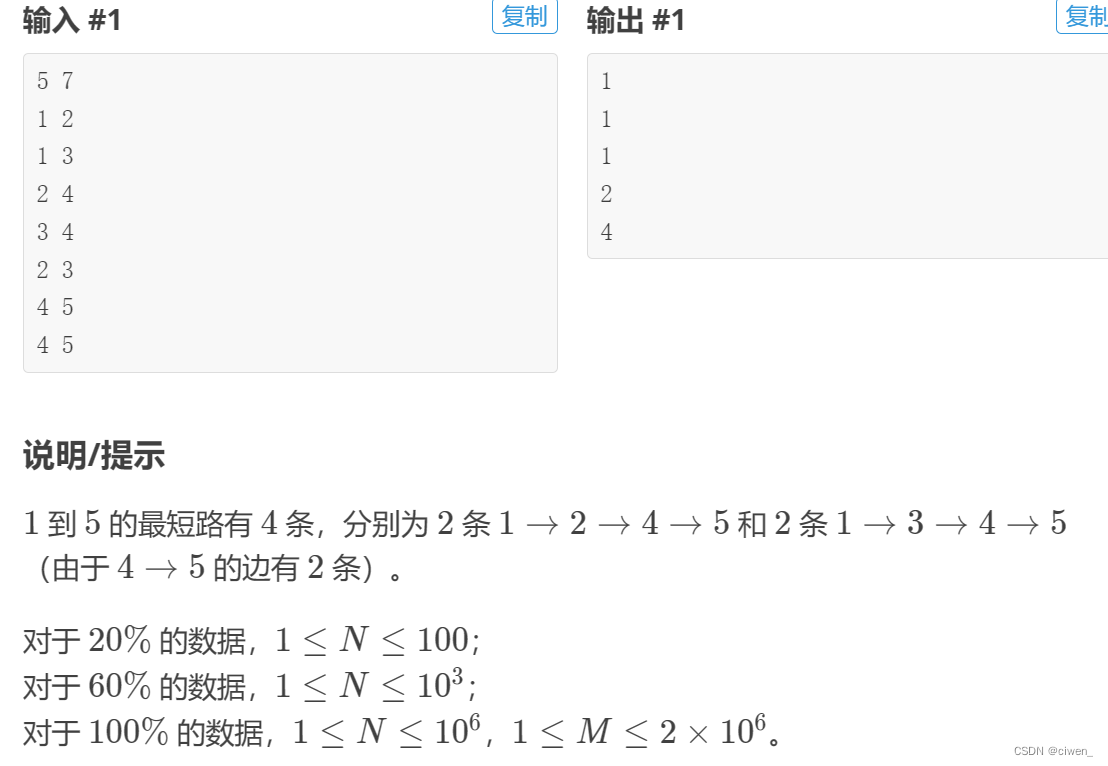

neuq-acm预备队训练week 8 P1144 最短路计数

题目描述

给出一个 N 个顶点 M条边的无向无权图,顶点编号为 1∼N。问从顶点 1 开始,到其他每个点的最短路有几条。

题目限制 输入格式

第一行包含 22 个正整数 N,M,为图的顶点数与边数。

接下来 M 行,每行 2个正整数 x,y&…

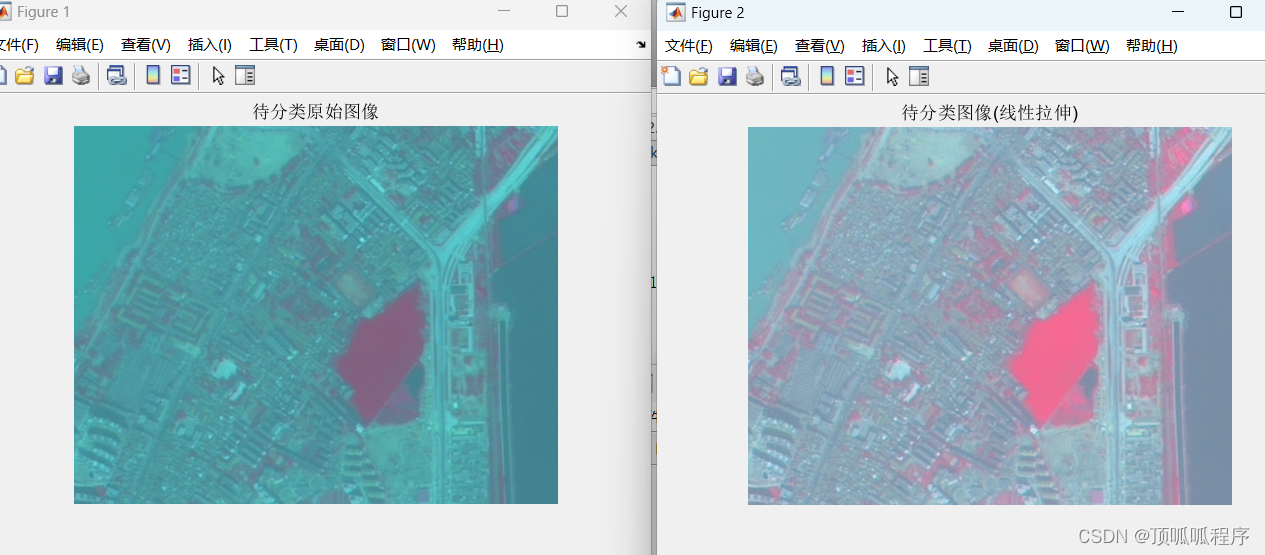

101基于matlab的极限学习机ELM算法进行遥感图像分类

基于matlab的极限学习机ELM算法进行遥感图像分类,对所获取的遥感图片进行初步分类和最终分类。数据可更换自己的,程序已调通,可直接运行。

键盘打字盲打练习系列之成为大师——5

一.欢迎来到我的酒馆 盲打,成为大师! 目录 一.欢迎来到我的酒馆二.关于盲打你需要知道三.值得收藏的练习打字网站 二.关于盲打你需要知道 盲打系列教程,终于写到终章了。。。一开始在看网上视频,看到up主熟练的打字技巧ÿ…

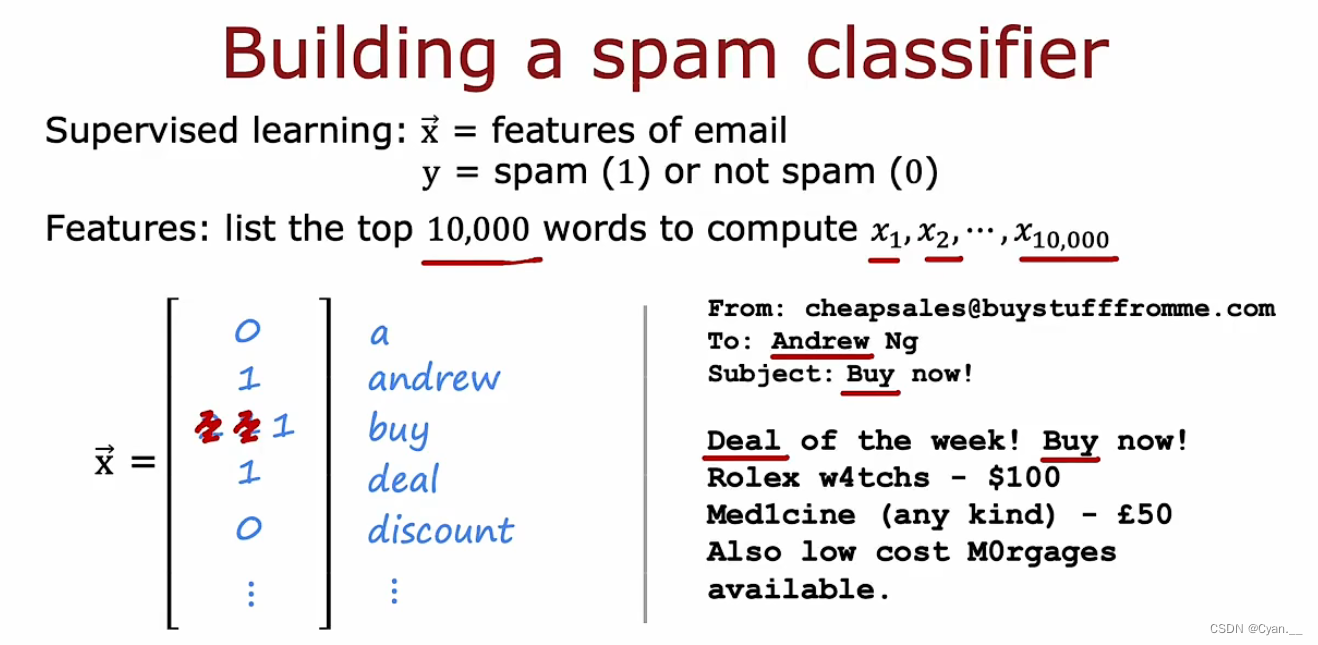

【机器学习】041_模型开发迭代过程

一、模型开发的一般步骤

1. 明确研究问题

确定问题的组成和结果,明晰问题是分类问题还是回归问题

2. 决定系统总体架构

①理解数据:采集(爬取)数据,生成(导入)数据,进行数据清洗…

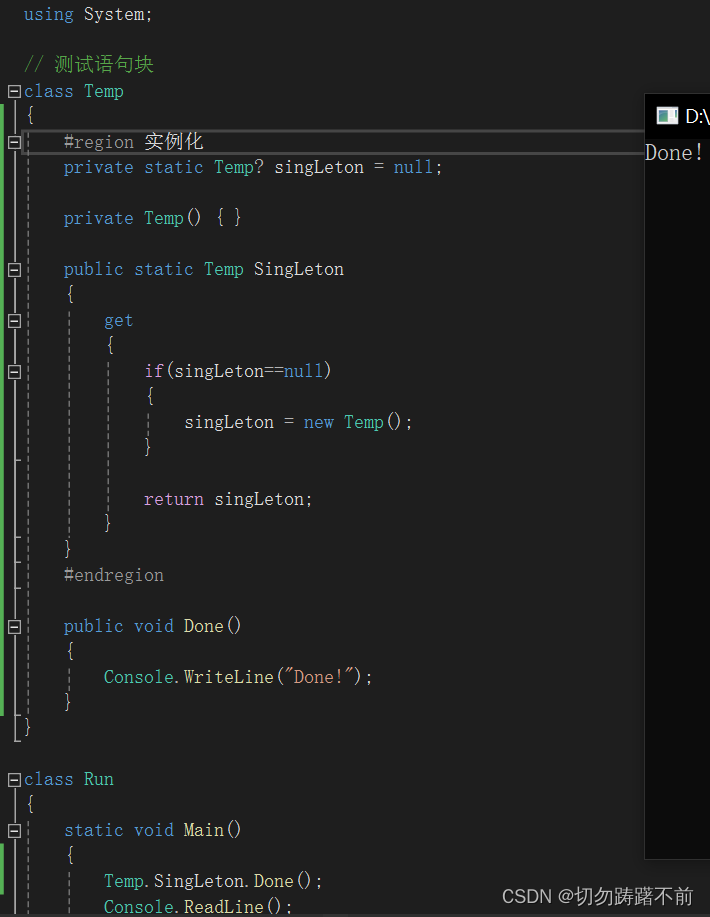

Unity 实现单例模式

目录 基本概念

饿汉模式(推荐)

懒汉模式: 基本概念

单例模式:类只有一个实例,一般使用static来实现单例模式; 比如:有一个Test类,实现了单例,假设这个唯一的实例名为SingTonle,实例在类内被实现并被stat…

【KCC@南京】KCC南京“数字经济-开源行”活动回顾录

11月26日,由KCC南京、中科南京软件研究所、傲空间、PowerData联合主办的 KCC南京“数字经济-开源行” 的活动已圆满结束。此次活动,3 场主题研讨,11 场分享,现场参会人数 60,线上直播观看 3000,各地小伙伴从…

代码随想录刷题题Day9

刷题的第九天,希望自己能够不断坚持下去,迎来蜕变。😀😀😀 刷题语言:C / Python Day9 任务 ● 20. 有效的括号 ● 1047. 删除字符串中的所有相邻重复项 ● 150. 逆波兰表达式求值

1 有效的括号 代码随想录…

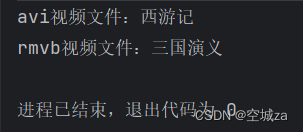

【设计模式--结构型--桥接模式】

设计模式--结构型--桥接模式 桥接(Bridge)模式定义结构案例好处使用场景 桥接(Bridge)模式

定义

将抽象与实现分离,使他们可以独立变化。它是用组合关系代替继承关系来实现,从而降低了抽象和实现这两个维…

轻量封装WebGPU渲染系统示例<46>- 材质组装管线(MaterialPipeline)灯光、阴影、雾以及多Pass(源码)

当前示例源码github地址:

https://github.com/vilyLei/voxwebgpu/blob/feature/material/src/voxgpu/sample/MaterialPipelineMultiPasses.ts

当前示例运行效果: 此示例基于此渲染系统实现,当前示例TypeScript源码如下:

export class MaterialPipelin…

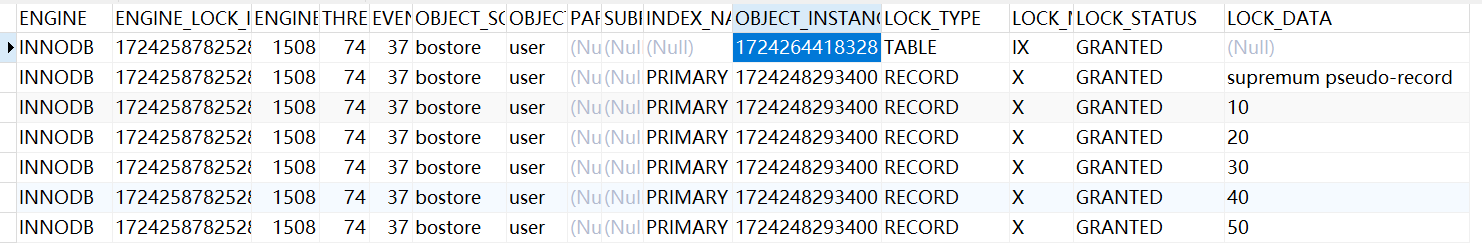

MySQL行锁范围分析(行锁、间隙锁、临键锁)

MySQL 中锁的概念

排它锁(Exclusive Lock)

X 锁,也称为写锁,若事务T对对象A加上X锁,则只允许T读取和修改A,其他任何事物都不能再对A 加任何锁,直到T释放A上的锁。 SELECT…FOR UPDATE 对读取的…

公务员国考省考小白需知

文章目录:

一:分类

1.国考

2.省考

二:必备途径

1.相关网站

1.1 官网

1.1.1 必须知道的

1.1.2 比较好用的

1.1.3 事业单位的

1.2 机构

1.3 时事

1.4 资源

1.5 题库

1.6 真题

2.相关公主号

3.应用

4.群聊如何找

三…

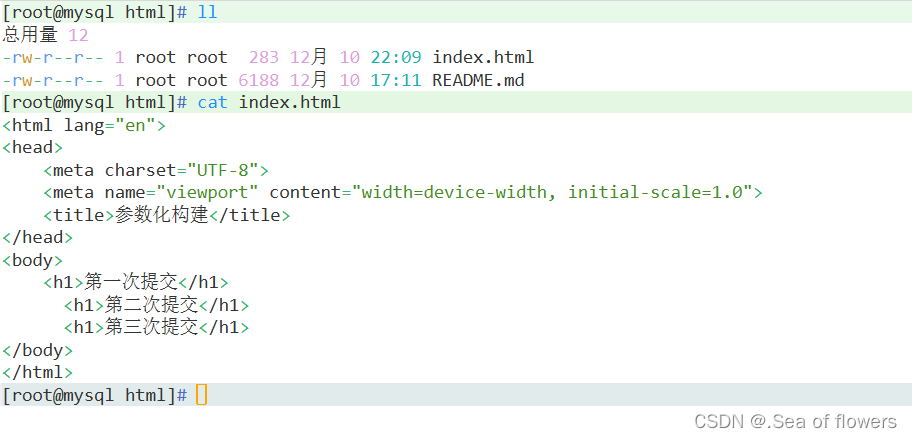

Jenkins参数化构建及代码发布

如何使用gitlab--web端可以观看此篇教程

https://blog.csdn.net/m0_59933574/article/details/134528050?spm1001.2014.3001.5502https://blog.csdn.net/m0_59933574/article/details/134528050?spm1001.2014.3001.5502

整体思路 依赖环境及工具 Git Centos7及以上 Gitla…

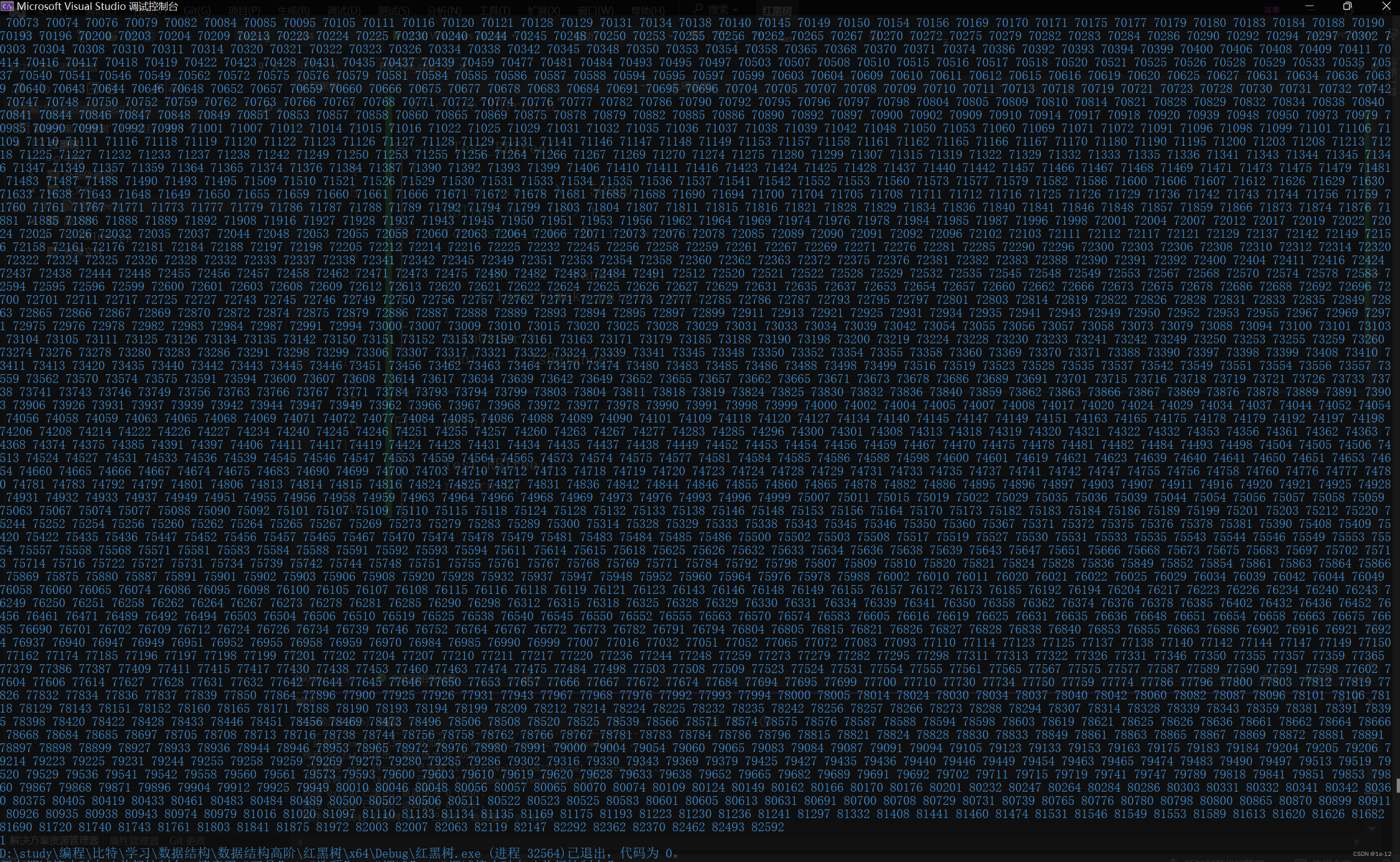

【数据结构高阶】红黑树

目录

一、红黑树的概念

二、红黑树的性质

2.1 红黑树与AVL树的比较

三、红黑树的实现

3.1 红黑树节点的定义

3.2 数据的插入

3.2.1 红黑树的调整思路

3.2.1.1 cur为红,f为红,g为黑,u存在且为红

3.2.1.2 cur为红,f为红&am…

php实现截取姓名中的第一个字作为头像的实战记录

php 截取中文字符串第一个字

substr 函数

在 PHP 中,使用 substr 函数来截取中文字符串的第一个字。由于 PHP 默认的字符编码是 UTF-8,它可以正确处理中文字符。

$chineseString "你好世界";

$firstChar substr($chineseString, 0, 1);

e…

【小白专用】Apache2.4+PHP8.3+MYSQL的配置

1.下载PHP和Apache 1、PHP下载

PHP For Windows: Binaries and sources Releases 注意:

1.使用Apache作为服务器的话,一定要下载Thread Safe的,否则没有php8apache2_4.dll这个文件, 如果使用IIS的请下载 NON Tread safe的 2.如果…

简单聊聊使用lombok 的争议

大家好,我是G探险者。

项目里,因为我使用了Lombok插件,然后代码走查的时候被领导点名了。 我心想,这么好用的插件,为啥不推广呢,整天写那些烦人的setter,getter方法就不嫌烦么? 领导…

最新文章

- 【基础架构篇九】《DeepSeek模型版本管理:Git+MLflow集成实践》

- 使用API有效率地管理Dynadot域名,为域名部署DNS安全拓展(DNSSEC)

- 【Leetcode 每日一题】2209. 用地毯覆盖后的最少白色砖块

- Hutool - Cache:简单而强大的缓存实现

- Lua C API :lua_insert 函数详解

- UE5从入门到精通之多人游戏编程常用函数

- 全球云科技基础设施:亚马逊云科技的海外服务器网络如何演进

- HTML代码混淆技术:原理、应用和实现方法详解

- LeetCode解法汇总2866. 美丽塔 II

- LeetCode解法汇总823. 带因子的二叉树

- WordPress顶部管理工具栏怎么添加一二级自定义菜单?

- 力扣解法汇总2418. 按身高排序